# **IQS269A DATASHEET**

8 Channel capacitive touch and proximity controller with additional Hall-effect and inductive sensing abilities.

#### 1 Device Overview

The IQS269A ProxFusion<sup>®</sup> IC is an 8-channel self/mutual-capacitive proximity and touch controller with best in class sensitivity, signal to noise ratio and power consumption. In addition, the device offers mixed sensing abilities such as Hall- and inductive sensing. Other features include automatic tuning and differential offset compensation for sense electrodes.

#### 1.1 Main Features

- > Highly flexible 8-channel ProxFusion® controller

- > Each channel can be configured with connections to up to 8 external connections OR one internal option

- > 8 external sensor pad connections:

- Self/Mutual-Capacitive sensors

- Self/Mutual Inductive sensors

- Dedicated reference sensor mode for environmental / mechanically sensitive designs

- > Internal sensor option:

- Hall-sensor

- > Serial scanning (Single ProxFusion® engine) up to 8 time-slots

- > Built-in basic functions:

- Automatic tuning

- Noise filtering

- Differential measurements (reference channels)

- Debounce & hysteresis

- Dual direction trigger indication

- > Built-in user-interface options

- Slider (up to 8 elements each) with co-ordinate output, flick/swipe/tap detection

- Up to two sliders may be defined

- Integrated measurement set for capacitance calculation

- > Wide Range of Capacitance Detection, Wide Electrode Range of 0 to 200 pF

- > Multiple custom signal level event triggers (e.g. proximity, touch, deep touch)

- > Capacitive resolution: down to 0.02fF

- > Automatic reference channel UIs for temperature and mechanical effects. Assign a reference channel to any single or group of sensing channels

- Options for reduced RF emissions for integration in RF sensitive environments (wide range of charge transfer frequency options)

- > I<sup>2</sup>C Interface with RDY interrupt line

- > Event mode (including reduced interrupt options: blocking & hysteresis)

- Assign a touch flag state of any channel to a dedicated GPIO (default: active low, open drain)

- > Dedicated address selection pin

- > Special pre-programmed options:

- Standalone operation on power-up (low-power single button touch)

- Active high output (push-pull)

- Timed long-press output (pulse after 5 second touch)

- > Supply voltage: 1.8V (-2%) to 3.6V

- > **Package options:** QFN16 (3 x 3 x 0.8mm), WLCSP-16 (1.62 x 1.62 x 0.5mm)

#### **1.2 Applications**

- > SAR compliance in mobile devices

- > Wear detection

- > Multi-slider & button designs

- > Low power wake-up buttons / proximity

- > HALL dock detection

#### **1.3 Description**

The IQS269A is a low-power microcontroller that features ProxFusion® technology for high-end proximity and touch applications. The IQS269A provides a highly integrated capacitive-touch solution with flexibility, unique combination sensing and long-term stability. The solution is specifically aimed at providing an accurate output to ensure safety and performance in mobile electronics.

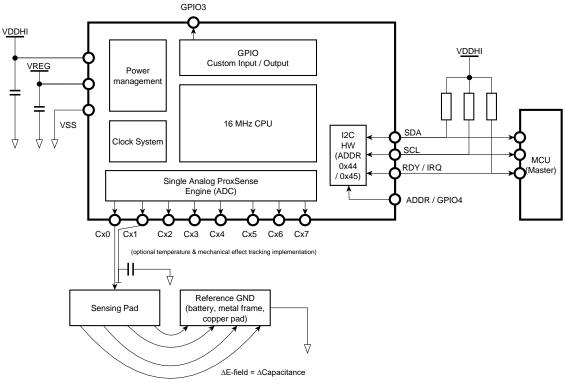

# 1.4 Block Diagram

Figure 1.1 Functional Block Diagram

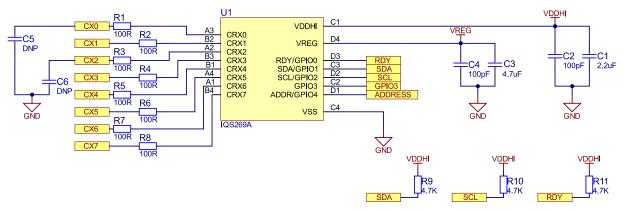

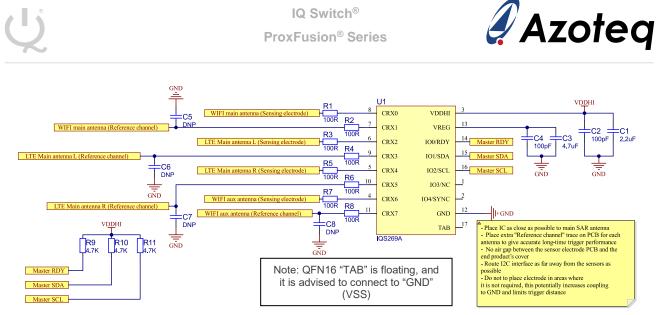

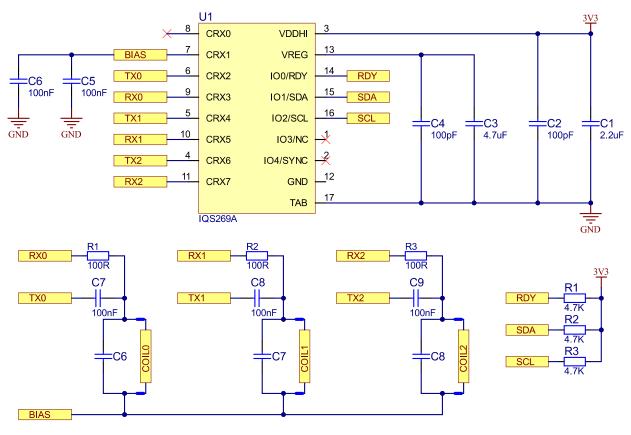

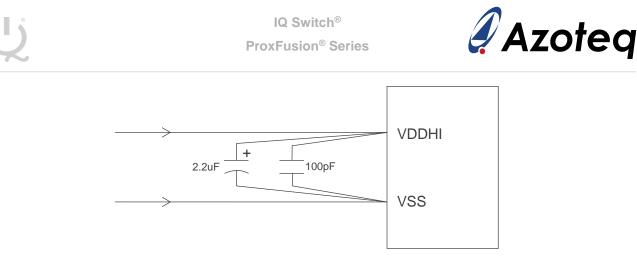

- The IQS269A has one main power pair of VDDHI and VSS that supplies digital and analog modules. Recommended bypass and decoupling capacitors are shown in Table 7.1

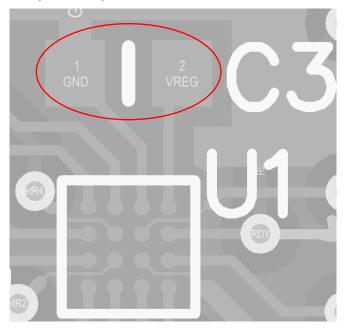

- VREG is the decoupling capacitor of the ProxFusion® regulator. The recommended value for the required decoupling capacitor is 4.7 μF, with a maximum ESR of ≤200 mΩ. Recommended VDDHI and VREG capacitor pairing is shown in section 7.3.5

- Add 100nF and 100pF to both VDDHI and VREG as required to ensure immunity against high frequency interference.

- See schematic diagram (section 7.2) for further and precise recommended circuit details.

#### Contents

| IQS269A DATASHEET                                                                                                                                                                                                                                                                                                                                                                                        |                                                                       | . 1                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-------------------------------------------------------------|

| 1 DEVICE OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                        |                                                                       | . 1                                                         |

| 1.2 Applications<br>1.3 Description                                                                                                                                                                                                                                                                                                                                                                      |                                                                       | 2<br>2                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                          | N                                                                     |                                                             |

| 2.2 QFN16 PIN DIAGRAM<br>2.3 PIN ATTRIBUTES                                                                                                                                                                                                                                                                                                                                                              |                                                                       | 6<br>7                                                      |

| 3 SPECIFICATIONS                                                                                                                                                                                                                                                                                                                                                                                         |                                                                       | . 8                                                         |

| <ul> <li>3.1.1 ESD Ratings</li> <li>3.1.2 Recommended Operating Conditions .</li> <li>3.1.3 Current Consumption</li> <li>3.1.4 Timing and Switching Characteristics .</li> <li>3.1.5 Reset Levels</li> <li>3.1.6 Miscellaneous Timings and Parameter</li> <li>3.1.7 Digital I/O Characteristics</li> </ul>                                                                                               | S                                                                     | 8<br>8<br>9<br>9<br>9<br>9                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                          | ······································                                |                                                             |

| <ul> <li>4.2 PERIPHERALS</li></ul>                                                                                                                                                                                                                                                                                                                                                                       | e Options                                                             | 11<br>12<br>12<br>12<br>13<br>14<br>14                      |

| 5 I <sup>2</sup> C INTERFACE                                                                                                                                                                                                                                                                                                                                                                             |                                                                       | 15                                                          |

| <ul> <li>5.2 I<sup>2</sup>C ADDRESS</li> <li>5.3 I<sup>3</sup>C COMPATIBILITY</li> <li>5.4 I<sup>2</sup>C READ</li> <li>5.5 I<sup>2</sup>C WRITE</li> <li>5.6 STOP-BIT DISABLE OPTION</li> <li>5.6.1 RDY Line Behaviour for Different Device</li> <li>5.7 WATCHDOG TIME-OUT</li> <li>5.8 CLOCK STRETCHING AND FORCING COMMUNIC</li> <li>5.8.1 IQS269A Clock Stretching During a Communication</li> </ul> | ce Versions<br>CATIONS.<br>CATIONS.<br>Communication Window (RDY Low) | 15<br>15<br>16<br>16<br><i>17</i><br>17<br>18<br><i>1</i> 8 |

|                                                                                                                                                                                                                                                                                                                                                                                                          | DNS                                                                   |                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                          | YOUT                                                                  |                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                       |                                                             |

| Copyright © Azoteg (Ptv) Ltd 2020.                                                                                                                                                                                                                                                                                                                                                                       | IQS269A Datasheet v1.6 Page 4                                         | of                                                          |

| 7.2 REFERENCE SCHEMATIC                                           |      |

|-------------------------------------------------------------------|------|

| 7.3 LAYOUT FUNDAMENTALS                                           |      |

| 7.3.1 Power Supply Decoupling                                     |      |

| 7.3.2 Transient Signal Management<br>7.3.3 ProxFusion® Peripheral | 26   |

| 7.3.3 Proxeusion® Periprieral                                     | .20  |

| 7.3.5 Recommended VREG and VDDHI capacitor ratio                  | .20  |

| 7.3.6 ESD Protection                                              |      |

| 7.3.7 Self-capacitance Electrode Design                           | .27  |

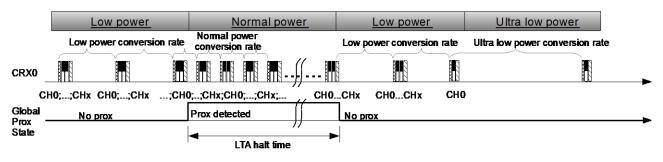

| 8 POWER MODE DESCRIPTION                                          | 28   |

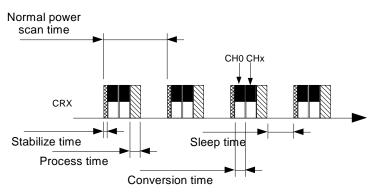

| 8.1 Normal Power (NP) Mode                                        | 28   |

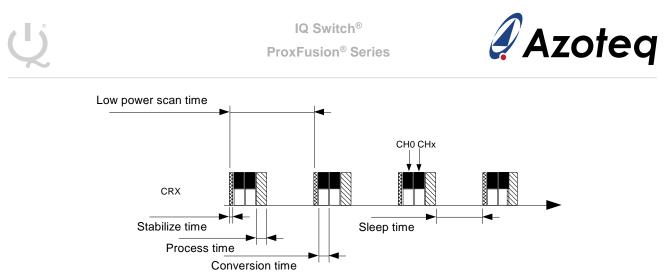

| 8.2 Low Power (LP) Mode                                           |      |

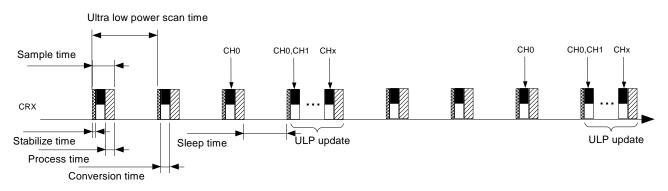

| 8.3 ULTRA-LOW POWER (ULP) MODE                                    |      |

| 9 HOW TO SETUP A HALL EFFECT SENSOR                               | . 30 |

| 10 HOW TO USE HALL BIN VALUES                                     | . 31 |

| 10.1 Overview                                                     | . 31 |

| 10.2 Calibration Process                                          |      |

| 11 HOW TO CONFIGURE SLIDERS                                       |      |

| 11.1 Registers to Configure                                       | 33   |

| 11.2 Gesture Descriptions                                         |      |

| 11.2.1 Tap                                                        |      |

| 11.2.2 Flick                                                      | 33   |

| 11.2.3 Swipe                                                      |      |

| 11.2.4 Hold                                                       | 34   |

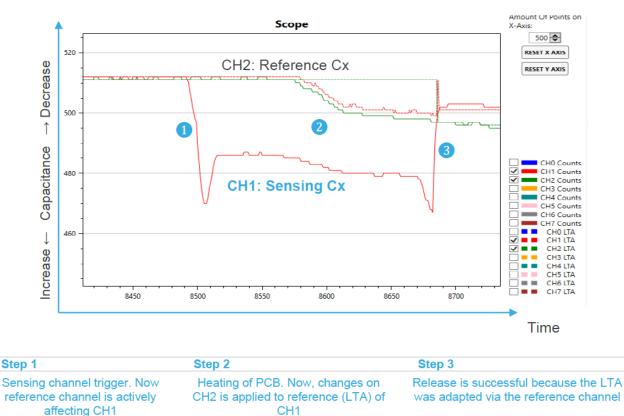

| 12 REFERENCE CHANNEL UIS                                          |      |

| 12.1 REFERENCE CHANNEL RESEED UI (DEFAULT)                        | 35   |

| 12.2 REFERENCE CHANNEL BLOCKING UI                                |      |

| 12.3 REFERENCE CHANNEL TRACKING UI                                | 36   |

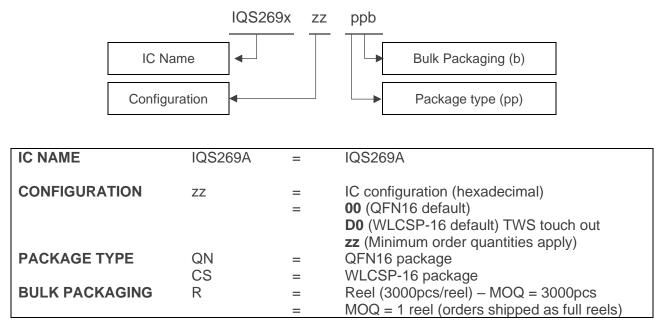

| 13 ORDERING INFORMATION                                           | 37   |

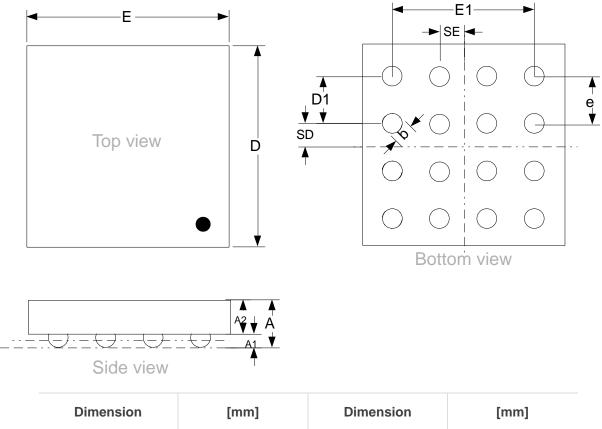

| 14 PACKAGE SPECIFICATION                                          | 38   |

| 14.1 PACKAGE OUTLINE DESCRIPTION – WLCSP16                        | 38   |

| 14.2 Package Outline Description – QFN16                          | 39   |

| 15 REVISION HISTORY                                               |      |

| APPENDIX A. MEMORY MAP DESCRIPTIONS                               | 42   |

# **2** Terminal Configuration and Function

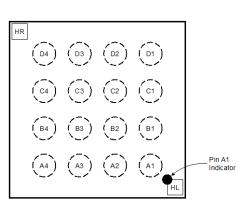

# 2.1 WLCSP16 Pin Diagram

| Pin no. | Signal name | Pin no. | Signal name  |

|---------|-------------|---------|--------------|

| A1      | CRX6        | C1      | VDDHI        |

| A2      | CRX2        | C2      | GPIO3        |

| A3      | CRX0        | C3      | SDA          |

| A4      | CRX5        | C4      | VSS          |

| B1      | CRX4        | D1      | ADDR / GPIO4 |

| B2      | CRX1        | D2      | SCL          |

| B3      | CRX3        | D3      | RDY          |

| B4      | CRX7        | D4      | VREG         |

| Area name     | Signal name                      | Area name     | Signal name                     |

|---------------|----------------------------------|---------------|---------------------------------|

| HR (internal) | HALL RIGHT<br>(FW setting: CRX0) | HL (internal) | HALL LEFT<br>(FW setting: CRX1) |

#### Figure 2.1 16-pin WLCSP Package (Top view)

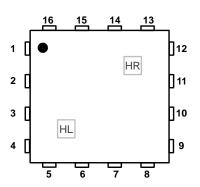

#### 2.2 QFN16 Pin Diagram

| Pin no. | Signal name  | Pin no. | Signal name    |

|---------|--------------|---------|----------------|

| 1       | GPIO3        | 9       | CRX3           |

| 2       | ADDR / GPIO4 | 10      | CRX5           |

| 3       | VDDHI        | 11      | CRX7           |

| 4       | CRX6         | 12      | VSS            |

| 5       | CRX4         | 13      | VREG           |

| 6       | CRX2         | 14      | RDY            |

| 7       | CRX1         | 15      | SDA            |

| 8       | CRX0         | 16      | SCL            |

|         |              | 17      | TAB - floating |

| I | Area name     | Signal name                      | Area name     | Signal name                     |

|---|---------------|----------------------------------|---------------|---------------------------------|

|   | HR (internal) | HALL RIGHT<br>(FW setting: CRX0) | HL (internal) | HALL LEFT<br>(FW setting: CRX1) |

Figure 2.2 16-pin QFN Package (Top view)

# 2.3 Pin Attributes

| Pin no. |       | Signal name  | Signal turnal            | Duffer ture | Power source | Reset state after |

|---------|-------|--------------|--------------------------|-------------|--------------|-------------------|

| WLCSP16 | QFN16 | Signal name  | Signal type <sup>1</sup> | Buffer type |              | BOR <sup>2</sup>  |

| A1      | 4     | CRX6         | Analog                   | LVCMOS      | VREG         | High-Z            |

| A2      | 6     | CRX2         | Analog                   | LVCMOS      | VREG         | High-Z            |

| A3      | 8     | CRX0         | Analog                   | LVCMOS      | VREG         | High-Z            |

| A4      | 10    | CRX5         | Analog                   | Analog      | VREG         | High-Z            |

| B1      | 5     | CRX4         | Analog                   | LVCMOS      | VREG         | High-Z            |

| B2      | 7     | CRX1         | Analog                   | LVCMOS      | VREG         | High-Z            |

| B3      | 9     | CRX3         | Analog                   | LVCMOS      | VREG         | High-Z            |

| B4      | 11    | CRX7         | Analog                   | Analog      | VREG         | High-Z            |

| C1      | 3     | VDDHI        | Р                        | Power       | N/A          | High-Z            |

| C2      | 1     | GPIO3        | I/O                      | LVCMOS      | VDDHI        | High-Z            |

| C3      | 15    | SDA          | I/O                      | LVCMOS      | VDDHI        | High-Z            |

| C4      | 12    | VSS          | Р                        | Power       | N/A          | High-Z            |

| D1      | 2     | ADDR / GPIO4 | I/O                      | LVCMOS      | VDDHI        | High-Z            |

| D2      | 16    | SCL          | I/O                      | LVCMOS      | VDDHI        | High-Z            |

| D3      | 14    | RDY          | 0                        | LVCMOS      | VDDHI        | High-Z            |

| D4      | 13    | VREG         | 0                        | Power       | VDDHI        | High-Z            |

|         | 17    | ТАВ          | Floating                 | N/A         | N/A          | N/A               |

#### Table 2.1 Pin Attributes

# 2.4 Signal Descriptions

#### Table 2.2 Signal Descriptions

| Function         | Cignal name  | Pin no. |       | Pin  | Description                                                                                          |

|------------------|--------------|---------|-------|------|------------------------------------------------------------------------------------------------------|

| Function         | Signal name  | WLCSP16 | QFN16 | type | Description                                                                                          |

|                  | CRX6         | A1      | 4     | I/O  |                                                                                                      |

|                  | CRX2         | A2      | 6     | I/O  |                                                                                                      |

|                  | CRX0         | A3      | 8     | I/O  |                                                                                                      |

| ProxFusion®      | CRX5         | A4      | 10    | I/O  | ProxFusion® channel                                                                                  |

| PIOXFUSION®      | CRX4         | B1      | 5     | I/O  |                                                                                                      |

|                  | CRX1         | B2      | 7     | I/O  |                                                                                                      |

|                  | CRX3         | B3      | 9     | I/O  |                                                                                                      |

|                  | CRX7         | B4      | 11    | I/O  |                                                                                                      |

| GPIO             | ADDR / GPIO4 | D1      | 2     | I/O  | I <sup>2</sup> C address selection (0x44 default, 0x45 with GPIO4 to VSS) / CH0 touch and hold PULSE |

| 0110             | GPIO3        | C2      | 1     | I/O  | Custom Touch Out / Sync In                                                                           |

|                  | SCL          | D2      | 16    | I/O  | I <sup>2</sup> C clock                                                                               |

| I <sup>2</sup> C | SDA          | C3      | 15    | I/O  | I <sup>2</sup> C data                                                                                |

|                  | RDY (IRQ)    | D3      | 14    | 0    | I <sup>2</sup> C event mode interrupt                                                                |

|                  | VDDHI        | C1      | 3     | Р    | Power supply                                                                                         |

| Power            | VREG         | D4      | 13    | 0    | ProxFusion® regulator external decoupling<br>capacitor                                               |

|                  | VSS          | C4      | 12    | Р    | Power ground                                                                                         |

<sup>1</sup> Signal Types: I = Input, O = Output, I/O = Input or Output

$^{2}$  High-Z = High-impedance with Schmitt trigger and pullup or pulldown (if available) disabled

## **3 Specifications**

# 3.1 Absolute Maximum Ratings

|                                                      | Min  | Мах                       | Unit |

|------------------------------------------------------|------|---------------------------|------|

| Voltage applied at VDDHI pin to VSS                  | -0.3 | +3.6                      | V    |

| Voltage applied to any ProxFusion® pin               | -0.3 | VREG                      | V    |

| Voltage applied to any other pin (referenced to VSS) | -0.3 | VDDHI + 0.3<br>(3.6V max) | V    |

| Storage temperature, T <sub>stg</sub>                | -40  | 125                       | °C   |

## 3.1.1 ESD Ratings

|                    |                         |                                                                                 | Value | Unit |

|--------------------|-------------------------|---------------------------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>1</sup>                 | ±4000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification<br>JESD22-C101 <sup>2</sup> | ±500  | V    |

# 3.1.2 Recommended Operating Conditions

|                        |                                                                          | min            | nom | max | Unit |

|------------------------|--------------------------------------------------------------------------|----------------|-----|-----|------|

| $V_{VDDHI_IN}$         | Supply voltage applied at VDDHI pin                                      | 1.764          |     | 3.6 | V    |

| $V_{VREG_OUT}$         | Regulator output at VREG                                                 | 1.62           |     | 1.7 | V    |

| VSS                    | Supply voltage applied at VSS pin                                        |                | 0   |     | V    |

| TA                     | Operating free-air temperature                                           | -40            |     | 85  | °C   |

| CVDDHI                 | Recommended capacitor at VDDHI <sup>3</sup>                              | 1 <sup>4</sup> | 2.2 | 10  | μF   |

| C <sub>VREG</sub>      | Recommended external buffer capacitor at VREG, ESR≤ 200mΩ                | 0.8            | 4.7 | 10  | μF   |

| C <sub>ELECTRODE</sub> | Maximum capacitance of all external electrodes on all ProxFusion® blocks | N/A            |     | 200 | pF   |

# **3.1.3 Current Consumption**

#### Table 3.1 Power Consumption for a Multi-channel Application (TWS)

| $\frac{\text{Device setup:}}{f_{\text{SYS}} = 16\text{MHz}}$ CH0 [wake-up] = self (500kHz, 512 target);<br>CH1 [wear] = self (500kHz, 512 target);<br>CH2 [reference] = self (500kHz, 512 target);<br>CH7 [unipolar] = Hall (4MHz; 512 target) |                            |     |                     |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----|---------------------|--|--|--|

| Event mode: No activation                                                                                                                                                                                                                      | u                          | A   | Report timing:      |  |  |  |

| Operating voltage:                                                                                                                                                                                                                             | 3.3V 1.8V                  |     |                     |  |  |  |

| Normal Power Mode                                                                                                                                                                                                                              | 185                        | 184 | 16ms                |  |  |  |

| Low Power Mode                                                                                                                                                                                                                                 | Low Power Mode 21 19 160ms |     |                     |  |  |  |

| Ultra-Low Power Mode         8.8         6.5         CH0: 160ms<br>(ULP update rate = 16*160ms = 2,56s)                                                                                                                                        |                            |     |                     |  |  |  |

| Halt Mode                                                                                                                                                                                                                                      | 2.9                        | 1.3 | No sampling / Sleep |  |  |  |

$^3$  A capacitor tolerance of  $\pm 20\%$  or better is required

<sup>4</sup> See section 7.3.5 to select an appropriate value for your application. Select 2.2uF for general use and evaluation

$<sup>^1</sup>$  JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Pins listed as  $\pm4000$  V may actually have higher performance.

$<sup>^2</sup>$  JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. Pins listed as  $\pm 500$  V may actually have higher performance.

Table 3.2 Power Consumption for a Multi-channel Application (TWS) and Optimized Touch Wake-up

| $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |      |                                                    |  |  |  |  |  |  |

|-------------------------------------------------------|------|------|----------------------------------------------------|--|--|--|--|--|--|

| Event mode: No activation                             | u    | A    | Report timing:                                     |  |  |  |  |  |  |

| Operating voltage:                                    | 3.3V | 1.8V |                                                    |  |  |  |  |  |  |

| Normal Power Mode                                     | 162  | 161  | 16ms                                               |  |  |  |  |  |  |

| Low Power Mode                                        | 18   | 17   | 160ms                                              |  |  |  |  |  |  |

| Ultra-Low Power Mode                                  | 6.5  | 4.9  | CH0: 160ms<br>(ULP update rate = 16*160ms = 2,56s) |  |  |  |  |  |  |

| Halt Mode                                             | 2.9  | 1.3  | No sampling / Sleep                                |  |  |  |  |  |  |

# Table 3.3 Power Consumption for a Multi-channel Application (TWS) with Optimized Touch and Lower SystemFrequency

| $\label{eq:setup:} \frac{\text{Device setup:}}{f_{\text{SYS}} = 4\text{MHz}} \\ \text{CH0 [wake-up] = self (500kHz, 192 target);} \\ \text{CH1 [wear] = self (500kHz, 512 target);} \\ \text{CH2 [reference] = self (500kHz, 512 target);} \\ \text{CH7 [unipolar] = Hall (1MHz; 320 target)} \\ \end{array}$ |      |      |                                                    |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|----------------------------------------------------|--|--|--|--|--|--|

| Event mode: No activation                                                                                                                                                                                                                                                                                     | u    | A    | Report timing:                                     |  |  |  |  |  |  |

| Operating voltage:                                                                                                                                                                                                                                                                                            | 3.3V | 1.8V |                                                    |  |  |  |  |  |  |

| Normal Power Mode                                                                                                                                                                                                                                                                                             | 174  | 172  | 16ms                                               |  |  |  |  |  |  |

| Low Power Mode                                                                                                                                                                                                                                                                                                | 21   | 19   | 160ms                                              |  |  |  |  |  |  |

| Ultra-Low Power Mode                                                                                                                                                                                                                                                                                          | 5.5  | 3.9  | CH0: 160ms<br>(ULP update rate = 16*160ms = 2,56s) |  |  |  |  |  |  |

| Halt Mode                                                                                                                                                                                                                                                                                                     | 2.9  | 1.3  | No sampling / Sleep                                |  |  |  |  |  |  |

# 3.1.4 Timing and Switching Characteristics

#### 3.1.5 Reset Levels

|                        |                                                      | Min | Тур | Max  | Unit |

|------------------------|------------------------------------------------------|-----|-----|------|------|

| V <sub>BOR, safe</sub> | Safe BOR power down level <sup>1</sup>               | 0.6 |     |      | V    |

| V <sub>VDDHI_BOD</sub> | Power-up/down level (Reset trigger) – slope > 100V/s |     |     | 1.7  | V    |

| $V_{VREG_BOD}$         | Power-up/down level (Reset trigger) – slope > 100V/s |     |     | 1.55 | V    |

# **3.1.6 Miscellaneous Timings and Parameters**

|                    |                                                                              | Min | Тур | Max | Unit |

|--------------------|------------------------------------------------------------------------------|-----|-----|-----|------|

| f <sub>xfer</sub>  | f <sub>xter</sub> Charge transfer frequency (derived from f <sub>SYS</sub> ) |     |     | +2% | N/A  |

| Isleep             | Sleep mode current                                                           |     |     | 1   | uA   |

| t <sub>WDT16</sub> | Watchdog timer for f <sub>SYS</sub> =16MHz                                   | 30  | 33  | 36  | ms   |

| t <sub>WDT4</sub>  | Watchdog timer for f <sub>SYS</sub> =4MHz                                    | 118 | 131 | 145 | ms   |

<sup>1</sup> A safe BOR can be correctly generated only if VDDHI drops below this voltage before it rises.

# 3.1.7 Digital I/O Characteristics

|                 |                                  | min            | nom | max            | Unit |

|-----------------|----------------------------------|----------------|-----|----------------|------|

| V <sub>IL</sub> | Input low level voltage          | VSS –<br>0.3   |     | 0.3 *<br>VDDHI | V    |

| V <sub>IH</sub> | Input high level voltage         | 0.7 *<br>VDDHI |     | VDDHI<br>+0.3  |      |

| V <sub>OL</sub> | Output low level voltage (@10mA) |                |     | 0.3            | V    |

| V <sub>OH</sub> | Output low level voltage (@5mA)  | VDDHI-<br>0.3  |     |                | V    |

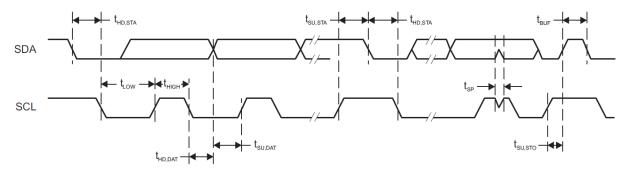

# 3.1.8 I<sup>2</sup>C Characteristics

Specified over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted).

|                     | PARAMETER                                           | TEST<br>CONDITIONS                                         | VDDHI      | MIN                         | ТҮР   | MAX   | UNIT |  |

|---------------------|-----------------------------------------------------|------------------------------------------------------------|------------|-----------------------------|-------|-------|------|--|

| f <sub>SYS</sub>    | System clock frequency                              |                                                            |            | 15.68                       | 16    | 16.32 | MHz  |  |

| f <sub>SCL</sub>    | SCL clock frequency                                 |                                                            | 1.8 V, 3 V | 0                           | 0 400 |       | kHz  |  |

| t <sub>HD,STA</sub> | Hold time (repeated) START                          | f <sub>SCL</sub> = 100 kHz<br>f <sub>SCL</sub> > 100 kHz   | 1.8 V, 3 V | <b>4.0</b><br>0.6           |       |       | μs   |  |

| t <sub>SU,STA</sub> | Setup time for a repeated START                     | f <sub>SCL</sub> = 100 kHz<br>f <sub>SCL</sub> > 100 kHz   | 1.8 V, 3 V | <b>4.7</b><br>0.6           |       |       | μs   |  |

| t <sub>HD,DAT</sub> | Data hold time                                      |                                                            | 1.8 V, 3 V | 0                           |       | ns    |      |  |

| t <sub>SU,DAT</sub> | Data setup time                                     |                                                            | 1.8 V, 3 V | 250                         |       |       | ns   |  |

| t <sub>su,sto</sub> | Setup time for STOP                                 | $f_{SCL} = 100 \text{ kHz}$<br>$f_{SCL} > 100 \text{ kHz}$ | 1.8 V, 3 V | 8 V, 3 V 4.0<br>0.6         |       | μs    |      |  |

| t <sub>SP</sub>     | Pulse duration of spikes suppressed by input filter | N/A                                                        | 1.8 V, 3 V | No pulse suppression filter |       | ns    |      |  |

Figure 3.1 I<sup>2</sup>C Mode Timing

#### **4 Detailed Description**

#### 4.1 Overview

The IQS269A solution boasts an integrated charge-transfer ProxFusion® technology coupled a lowpower flexible MCU. The IQS269A features up to 8 self/projected-capacitance channels with proximity sensing (down to 0.02-fF resolution). This flexible solution offers custom combinations of sensing channels including dedicated tracking channels for environmental and material effects.

#### 4.2 Peripherals

#### 4.2.1 ProxFusion®

The ProxFusion® module detects the capacitance changed with a charge-transfer method. In lowest power modes, the ProxFusion® module can periodically wake the CPU based on a ProxFusion® timer source. The ProxFusion® module supports the following proximity-sensing capability:

- Up to 8 ProxFusion® individual sensors composed of a single analogue ProxFusion® block. This block consists of 8 I/Os, and sensing is executed sequentially in 8 time-slots.

- Each timeslot (channel) can be configured to do self-capacitance measurements on a single I/O or projected capacitance measurement on a pair of I/Os

- Each channel can be configured to be a self-contained measurement channel or pair with other channels as a reference measurement for mechanical or temperature effects.

- Supports a wake-on-proximity state machine.

- Processing logic to perform normal filter calculation and optimized threshold detection for mobile device SoCs (multiple levels and interrupt frequency limiting).

- Automated processing for custom differential pairs (reference measurement channels) when sensor traces are exposed to temperature sensitive materials or mechanical variation.

# 4.3 User Interface Options

User interface options refer to "pre-programmed" OTP (one-time-programmable) options for the IQS269A. See <u>ordering information</u>. These options will cause the IC to power-up in a specific state.

# 4.3.1 Default Option ('00')

In default, the IQS269A will start with:

- No sensing active (All Cx sensor pins will be inactive)

- Sensor processor will be waiting for initialization

- The IRQ (RDY) pin will indicate windows for communication from master

- GPIO3 will be touch output for CH0 (once IC reset is acknowledged <u>ACK\_RESET</u>)

- and GPIO4 will be an input to adjust the <u>I<sup>2</sup>C address</u>.

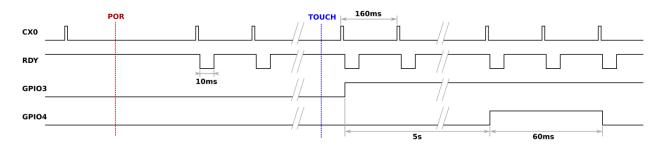

# 4.3.2 TWS Option ('D0')

In the TWS option, the IQS269A will start with:

- Sensing active on CRX0, assigned to CH0, 160ms sampling rate (All other CRX sensor pins will be inactive)

- Sensor processor will be sensing while waiting for initialization

- The RDY pin will indicate windows for communication from master

- GPIO3 will be touch output for CH0 from the POR event

- and GPIO4 will output a single pulse for indication of a prolonged touch (>5seconds) on CH0

- Known issue and workaround: see in appendix

Figure 4.1 Alternative Standalone POR Protocol

GPIO3 will give a direct, active high output of the touch response on the CRX0 pin. GPIO4 will serve as a delayed single output pulse, only sending an active high pulse when the touch condition lasts for 5 seconds.

With this user interface running on CRX0, the IC is still fully usable in the I<sup>2</sup>C mode with RDY indications for IC initialization and normal runtime use.

#### 4.3.3 Additional Non-standard Programmable Options

- Ordering code example: IQS269AzzCSR (special order MOQs apply)

- First "z" (right side): Bank0 bits 7,6,1,0 [IQS269AzzCSR]

- Second "z" (left side): Bank5 bits 3,2,1,0 [IQS269AzzCSR]

- Bank 1-4 is accessible for custom calibration data

| OTP<br>Bank                            | Bit 7                               | 6                       | 5            | 4                                   | 3                        | 2                  | 1      | Bit 0   |  |  |  |

|----------------------------------------|-------------------------------------|-------------------------|--------------|-------------------------------------|--------------------------|--------------------|--------|---------|--|--|--|

| Bank 0                                 | f <sub>SYS</sub> =4MHz<br>not 16MHz | Sleep during<br>RDY low |              | I <sup>2</sup> C address (reserved) |                          |                    |        |         |  |  |  |

| Bank 1<br>(loaded to<br>0x35 offset 0) |                                     | HALL bin                | (Left – Cx1) | ft – Cx1) HALL bin (Right – Cx0)    |                          |                    |        |         |  |  |  |

| Bank 2<br>(loaded to<br>0x35 offset 1) |                                     | Reserved                |              |                                     |                          |                    |        |         |  |  |  |

| Bank 3<br>(loaded to<br>0x36 offset 0) |                                     |                         |              | Re                                  | served                   |                    |        |         |  |  |  |

| Bank 4<br>(loaded to<br>0x36 offset 1) |                                     |                         |              | Re                                  | served                   |                    |        |         |  |  |  |

| Bank 5                                 |                                     | Res                     | erved        |                                     | GPIO4 output<br>not ADDR | GPIOs PP<br>not OD | Startu | ıp type |  |  |  |

| Bank 6                                 |                                     | Res                     | erved        |                                     |                          | Rese               | erved  |         |  |  |  |

| Bank 7                                 |                                     | Res                     | erved        |                                     |                          | Rese               | erved  |         |  |  |  |

#### General options (special order):

Bank0 [1:0]:

- 00: 0x44 (if Bank5 [3] cleared: GPIO4 pull-down = address 0x45)

- 01: 0x45 (if Bank5 [3] cleared: GPIO4 pull-down = address 0x44)

- 10: 0x46 (if Bank5 [3] cleared: GPIO4 pull-down = address 0x47)

- 11: 0x47 (if Bank5 [3] cleared: GPIO4 pull-down = address 0x46)

#### Start-up type (special order):

Bank5 [1:0]:

- 00: No conversions wait for host to setup

- 01: One touch channel active (most sensitive)

- 10: One touch channel active (less sensitive)

- 11: One touch channel active (least sensitive)

Bank5 [2]:

- 0: Open drain (active low)

- 1: Push-pull (active high)

#### Bank5 [3]:

- 0: GPIO4 for address

- 1: GPIO4 for touch and hold output

# 4.4 Identification

## 4.4.1 Revision Identification

The device revision information is included as part of the top-side marking on the device package as shown below. The hardware revision is also stored as shown in the table below:

| Description                                          | Address | offset 0                                                           | offset 1                                                                                                                                  |  |  |

|------------------------------------------------------|---------|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Product number, Version number 00h 2 bytes)          |         | 0x4F – IQS269A                                                     | 0x01 – device version 0 (pre-production)<br>0x02 – device version 1 (production - obsolete)<br>0x03 – device version 2 and 3 (production) |  |  |

| Hardware revision, Minor FW<br>revision<br>(2 bytes) | 01h     | 0x0D or 0x4D – device version 2<br>0x2D or 0x6D – device version 3 |                                                                                                                                           |  |  |

## 4.4.2 WLCSP16 Device Identification

The device type can be identified from the top-side marking on the device package as shown below:

|              | 269A = device name (IQS269)                                                                                     |

|--------------|-----------------------------------------------------------------------------------------------------------------|

| 269A         | zz = configuration / xx = batch code (AA, AB ZZ)                                                                |

| zzxx<br>vppp | v = IC version number (0 - Pre-production, 1 - Production obsolete, 2 - Production, 3,4 - Production; see PCNs) |

| •            | ppp = product code                                                                                              |

|              | • = Pin A1 indicator                                                                                            |

## 4.4.3 QFN16 Device Identification

The device type can be identified from the top-side marking on the device package as shown below:

|          | IQS269A = device name                                                                                                            |

|----------|----------------------------------------------------------------------------------------------------------------------------------|

| Azoteq   | zz = configuration                                                                                                               |

| 269Azzxx | xx = batch code                                                                                                                  |

| vppp     | v = IC version number (e – Engineering, 0 – Pre-production, 1 – Production – obsolete, 2 – Production, 3 – Production; see PCNs) |

|          | ppp = Product code                                                                                                               |

|          | • = Pin A1 indicator                                                                                                             |

# **5 I<sup>2</sup>C Interface**

## 5.1 I<sup>2</sup>C Module Specification

The device supports a standard two wire I<sup>2</sup>C interface with the addition of an RDY (ready interrupt) line. The communications interface of the IQS269A supports the following:

- *Fast-mode (Fm)* standard I<sup>2</sup>C up to 400kHz.

- Streaming data as well as event mode.

- The master may address the device at any time. If the IQS269A is not in a communication window, address polling will be acknowledged immediately with minimal clock stretching.

- The provided interrupt line (RDY) is an open-drain active low implementation and indicates a communication window.

The IQS269A implements 8bit addressing with 2 bytes at each address. Two consecutive read/writes are required in this memory map structure. The two bytes at each address will be referred to as "byte 0" and "byte 1".

# 5.2 I<sup>2</sup>C Address

The IQS269A (order code: IQS269A00CSR / IQS269A00QNR) offers 2 address options:

- Default: 0x44

- Float GPIO4 (Internal pull-up defined)

- Alternate: 0x45

- o GND GPIO4

Other address options exist on special request. Please contact Azoteq.

The order codes: IQS269AD0CSR / IQS269AD0QNR have a fixed I<sup>2</sup>C address of 0x44 with no alternate option.

# 5.3 I<sup>3</sup>C Compatibility

This device is not compatible with an I<sup>3</sup>C bus due to clock stretching allowed for data retrieval.

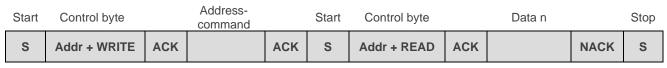

#### 5.4 I<sup>2</sup>C Read

To read from the device a *current address read* can be performed. This assumes that the addresscommand is already setup as desired.

#### Current Address Read

| Start | Control byte |     | Data n |     | Data n+1 |      | Stop |

|-------|--------------|-----|--------|-----|----------|------|------|

| S     | Addr + READ  | ACK |        | ACK |          | NACK | S    |

#### Figure 5.1 Current Address Read

If the address-command must first be specified, then a *random read* must be performed. In this case, a WRITE is initially performed to setup the address-command, and then a repeated start is used to initiate the READ section.

IQ Switch<sup>®</sup> ProxFusion<sup>®</sup> Series

#### Random Read

Figure 5.2 Random Read

# 5.5 I<sup>2</sup>C Write

To write settings to the device a *Data Write* is performed. Here the Address-Command is always required, followed by the relevant data bytes to write to the device.

#### Data Write

| Start | Control byte |     | Address-<br>Command |     | Data n |     | Data n+1 |     | Stop |

|-------|--------------|-----|---------------------|-----|--------|-----|----------|-----|------|

| S     | Addr + WRITE | ACK |                     | ACK |        | ACK |          | ACK | S    |

Figure 5.3 PC Data Write

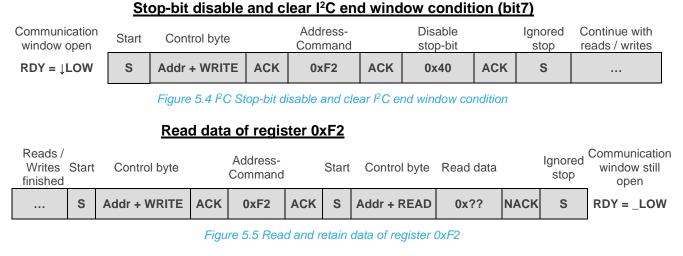

# 5.6 Stop-bit Disable Option

For specific I<sup>2</sup>C master limitations, the IQS269A offers the following:

- I<sup>2</sup>C settings register (0xF2) for stop-bit disable functionality,

- The "stop bit disable" bit for ignoring the I<sup>2</sup>C stop condition from the master. This "ignore" will keep the communication window open.

- The "I<sup>2</sup>C end window" condition bit making it possible to set the "stop-bit enable" only once.

- The command will cause the communication window to close only at the next stopbit sent from the master.

- The benefit from using this command is that the "stop-bit disable" does not need to be enabled again at the next communication window.

- All settings written before and after setting this bit will be applied as long as it is written before any stop bit is sent from the master.

- The RDY timeout period register (0x85, offset 0) can be used for an automatic time-out. The timer will start from the last byte on the bus. In this case no intervention from the master is required to end the communications window.

Customers using an MCU with a binary serial-encoder peripheral which is not fully I<sup>2</sup>C compatible (but provide some crude serial communication functions) can use this option to configure the IQS269A so that any auto generated stop command from the serial peripheral can be ignored by the IQS269A I<sup>2</sup>C hardware. This will restrict the IQS269A from immediately exiting a communication window during event mode (reduced communication only for events) until all required communication has been completed and a stop command can correctly be transmitted. Please refer to the figures below for serial data transmission examples.

Please note:

- Stop-bit disable and I<sup>2</sup>C end window condition clearing must be performed at the beginning and of a communication window. The first I<sup>2</sup>C register to be written to ensure no unwanted communication window termination.

- Leaving the Stop-bit disabled will result in successful reading and writing of registers but will not execute any commands written over I<sup>2</sup>C in a communication window being terminated after a RDY timeout and with no IQS recognised stop command.

- 3. The default RDY timeout period for IQS269A is purposefully long (10.24ms) for slow responding MCU hardware architectures. Please set this register according to your requirements/preference.

- 4. Use the I<sup>2</sup>C end window condition (0xF2, bit7) to purposefully terminate at the next stop-bit condition generated by the master.

- 5. For any following I<sup>2</sup>C communication windows, repeat the sequence of first clearing the I<sup>2</sup>C end window condition (0xF2, bit7) to prevent exit of the communication window before reading data from applicable event and channel registers.

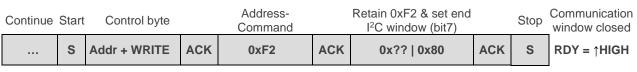

# Modify-write register 0xF2

Figure 5.6 Modify-write register 0xF2 to end the communication window

# 5.6.1 RDY Line Behaviour for Different Device Versions

The IQS269A RDY line behaviour will differ for device version 2 and 3.

- In IQS269A v2, the RDY signal will remain low (even if Stop conditions is issued and ignored by IQS269A) and will only go high after an *I2C end window* command have been issued (or RDY timeout is reached).

- In IQS269A v3, the RDY signal will toggle high immediately when a Stop condition is issued (regardless of using stop condition handling active) but the communication window (internally at IQS269A) will remain open. The I2C end comms command (0xF2 = 0xC1) will close the communication window (or the window will also close if the RDY timeout is reached).

# 5.7 Watchdog Time-out

The IQS269A is designed to do a watchdog reset if:

- I<sup>2</sup>C stuck during transmission (number of clock pulses is not a multiple of 9)

- IQS269A was addressed but no further communication initiated, ie, no I<sup>2</sup>C events happen (no data, no stop or no start)

- I<sup>2</sup>C bus remain low shortly after POR

- I<sup>2</sup>C reset command is called.

• Program flow does not execute as expected (or goes wrong due to something like damaged ROM memory)

The IQS269A program flow waits and does NOT reset in the following cases:

- If VREG does not stabilize

- If the zero-cross sync UI is running and there is no sync signal

- If the IC is in test mode (for IC testing or IC OTP programming)

# 5.8 Clock Stretching and Forcing Communications

Communications with the IQS269A can be forced by addressing the IQS269A and waiting for an acknowledgement (ACK) to be returned after clock stretching the host. The following situations will result in forced communications:

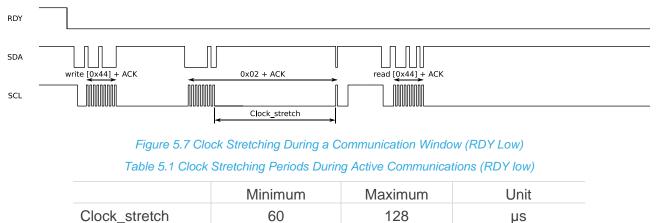

# 5.8.1 IQS269A Clock Stretching During a Communication Window (RDY Low)

When the RDY signal is already low, to report periodic sampled data (streaming mode) or to indicate an event occurrence (event mode), the IQS269A will stretch the clock line (SCL) after the master has written the address command byte to the device. The clock stretch can be attributed to the IQS269A loading data from the buffer. Clock stretching will be induced each time configuring a new address command byte occurs. The timing diagram for this occurrence is shown below in Figure 5.7.

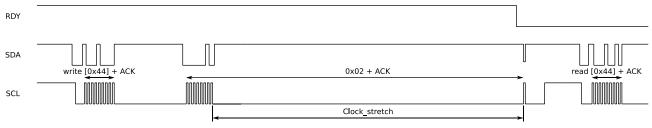

# 5.8.2 Clock Stretching When MCU Polls IQS269A Without Waiting for RDY Event

The IQS269A will stretch the clock if the master addresses the device outside of a communication window (RDY high). Interrupting the device during ongoing sensor conversions, data processing or inactive (sleep) states will result in slightly longer clock stretching while the IQS269A terminates the task at hand and prepares the communication peripheral to respond. The timing diagram for the event is shown in Figure 5.8 below.

Figure 5.8 Clock Stretching During Inactive Communication (RDY high) Before Opening a Communication Window

Table 5.2 Clock Stretching Periods During Inactive Communications (RDY high)

|               | Typical | Maximum | Unit |

|---------------|---------|---------|------|

| Clock_stretch | 250     | 300     | μs   |

6 I<sup>2</sup>C Memory Map – Register Descriptions

#### Table 6.1 IQS269A Register Map Summary

| Full<br>address | Group name                         | ltem nan                              | ne (offset                                                                  | 0 – 8bits  | 5)                          |                  |                    |       |               | ltem nar                                                                    | ne (offset  | 1 – 8bits            | 5)          |             |                |       |               | Data<br>Access |

|-----------------|------------------------------------|---------------------------------------|-----------------------------------------------------------------------------|------------|-----------------------------|------------------|--------------------|-------|---------------|-----------------------------------------------------------------------------|-------------|----------------------|-------------|-------------|----------------|-------|---------------|----------------|

| 0x00            | Version Info                       | Bit 7<br>Product r                    | numbor                                                                      |            |                             | I                |                    |       | Bit 0         | Bit 7                                                                       | e version   |                      |             |             |                |       | Bit 0         | Read-          |

| 0,00            | Version Into                       |                                       | QS269A                                                                      |            |                             |                  |                    |       |               |                                                                             | sion info"  | link for so          | ftware rev  | vision data | aile           |       |               | Only<br>Read-  |

| 0x01            | -                                  |                                       | re number                                                                   | _          | _                           | _                | _                  | _     | _             |                                                                             | N revision  |                      | itware rev  |             | an5            | _     | _             | Only<br>Read-  |

| 0.001           |                                    |                                       | sion info" l                                                                |            | ftworo rov                  | ision data       | ile                |       |               |                                                                             | sion info"  |                      | ftwara ray  | vision data | aila           |       |               | Only<br>Read-  |

| 0.000           | Clabal flags                       |                                       |                                                                             |            |                             | ISION dela       | 115                |       |               |                                                                             |             |                      | itware iev  | ISION dela  | alis           |       |               | Only           |

| 0x02            | <u>Global flags</u>                | •                                     | Flags & Po                                                                  |            | -                           | . <u>.</u>       | I                  |       | h             |                                                                             | event flags |                      | 05050       | 1050        |                | TOUGH | <b>DDO</b> Y  | Read-<br>Only  |

|                 |                                    | Show<br>Reset                         | Reserved                                                                    | 1          | Power m<br>(see reg<br>5:4) | ode<br>0x80 bits | ATI in<br>progress | EVENT | ULP<br>UPDATE | POWER<br>MODE<br>CHANG<br>E                                                 | SYSTEM      | ENCE<br>CHAN-<br>NEL | ED          | TURE        | DEEP-<br>TOUCH | TOUCH | PROX          | Read-<br>Only  |

| 0x03            | <u>Slider event</u><br>flags       | Gesture                               | (Slider1 &                                                                  | Slider 0)  | event flag                  | S                |                    |       |               | Reserve                                                                     | d           |                      |             |             |                |       |               | Read-<br>Only  |

|                 |                                    |                                       | FLICK FLICK HOLD_1 TAP_1 FLICK FLICK HOLD_0 TAP_<br>NEG_1 POS_1 NEG_0 POS_0 |            |                             |                  |                    |       | TAP_0         |                                                                             |             |                      |             |             |                |       | Read-<br>Only |                |

| 0x04            | Channel states                     |                                       | Channels Proximity state                                                    |            |                             |                  |                    |       |               | Channels Proximity direction state (for bi-directional triggers – enable in |             |                      |             |             |                |       | ole in        | Read-<br>Only  |

|                 |                                    | CH7 (bit 7) $\rightarrow$ CH0 (bit 0) |                                                                             |            |                             |                  |                    |       |               | 0x86)<br>CH7 (bit 7) → CH0 (bit 0)                                          |             |                      |             |             |                |       |               | Read-          |

| 0x05            | -                                  | Channels                              | Channels Touch state                                                        |            |                             |                  |                    |       |               | Channels Deep Touch state                                                   |             |                      |             |             |                |       |               | Only<br>Read-  |

|                 |                                    | CH7 (bit                              | CH7 (bit 7) $\rightarrow$ CH0 (bit 0)                                       |            |                             |                  |                    |       |               | CH7 (bit 7) $\rightarrow$ CH0 (bit 0)                                       |             |                      |             |             |                |       |               | Only<br>Read-  |

| 0x06            | -                                  | Referenc                              | e channel                                                                   | s actively | used                        |                  |                    |       |               | Reserve                                                                     | d           |                      |             |             |                |       |               | Only<br>Read-  |

|                 |                                    | CH7 (bit                              | $(7) \rightarrow CHC$                                                       | ) (bit 0)  |                             |                  |                    |       |               |                                                                             |             |                      |             |             |                |       |               | Only<br>Read-  |

| 0x07            |                                    | Reserved                              | d                                                                           |            |                             |                  |                    |       |               | Reserve                                                                     | d           |                      |             |             |                |       |               | Only<br>Read-  |

|                 |                                    |                                       |                                                                             |            |                             |                  |                    |       |               |                                                                             |             |                      |             |             |                |       |               | Only<br>Read-  |

|                 |                                    | LEAST S                               | SIGNIFICA                                                                   | NT BYT     | E                           |                  |                    |       |               | MOST SIGNIFICANT BYTE                                                       |             |                      |             |             |                |       |               | Only           |

| 0x08            | Raw Counts &<br>LTA                | FILTERE                               | D COUNT                                                                     | FS CHAN    | NEL 0 (LS                   | SB)              |                    |       |               | FILTERE                                                                     | D COUN      | TS CHAN              | NEL 0 (M    | SB)         |                |       |               | Read-<br>Only  |

| 0x09            |                                    | LONG TE                               | ERM AVE                                                                     | RAGE CH    | HANNEL (                    | (LSB)            |                    |       |               | LONG T                                                                      | ERM AVE     | RAGE CH              | HANNEL (    | ) (MSB)     |                |       |               | Read-<br>Only  |

| 0x0A            |                                    | FILTERE                               | D COUNT                                                                     | FS CHAN    | INEL 1 (LS                  | SB)              |                    |       |               | FILTERE                                                                     | D COUN      | TS CHAN              | NEL 1 (M    | SB)         |                |       |               | Read-<br>Only  |

| 0x0B            |                                    | LONG TE                               | ERM AVE                                                                     | RAGE CH    | HANNEL 1                    | (LSB)            |                    |       |               | LONG TERM AVERAGE CHANNEL 1 (MSB)                                           |             |                      |             |             |                |       |               | Read-<br>Only  |

| 0x0C            | -                                  | FILTERE                               | D COUNT                                                                     | LS CHAN    | NEL 2 (LS                   | SB)              |                    |       |               | FILTERED COUNTS CHANNEL 2 (MSB)                                             |             |                      |             |             |                |       |               | Read-<br>Only  |

| 0x0D            |                                    | LONG TE                               | ERM AVE                                                                     | RAGE CH    | HANNEL 2                    | (LSB)            |                    |       |               | LONG TERM AVERAGE CHANNEL 2 (MSB)                                           |             |                      |             |             |                |       |               | Read-<br>Only  |

| 0x0E            |                                    | FILTERE                               | D COUNT                                                                     | FS CHAN    | NEL 3 (LS                   | SB)              |                    |       |               | FILTERED COUNTS CHANNEL 3 (MSB)                                             |             |                      |             |             |                |       |               | Read-          |

| 0x0F            | -                                  | LONG TE                               | ERM AVE                                                                     | RAGE CH    | HANNEL 3                    | (LSB)            |                    |       |               | LONG T                                                                      | ERM AVE     | RAGE CH              | HANNEL      | B (MSB)     |                |       |               | Only<br>Read-  |

| 0x10            | -                                  | FILTERE                               | D COUNT                                                                     | FS CHAN    | NEL 4 (LS                   | SB)              |                    |       |               | FILTERED COUNTS CHANNEL 4 (MSB)                                             |             |                      |             |             |                |       |               | Only<br>Read-  |

| 0x11            | -                                  | LONG TE                               | ERM AVE                                                                     | RAGE CH    | HANNEL 4                    | (LSB)            |                    |       |               | LONG TERM AVERAGE CHANNEL 4 (MSB)                                           |             |                      |             |             |                |       |               | Only<br>Read-  |

| 0x12            |                                    | FILTERE                               | D COUNT                                                                     | FS CHAN    | NEL 5 (LS                   | SB)              |                    |       |               | FILTERED COUNTS CHANNEL 5 (MSB)                                             |             |                      |             |             |                |       |               | Only<br>Read-  |

| 0x13            | -                                  | LONG TE                               | ERM AVE                                                                     | RAGE CH    | HANNEL 5                    | (LSB)            |                    |       |               | LONG T                                                                      | ERM AVE     | RAGE CH              | HANNEL S    | 5 (MSB)     |                |       |               | Only<br>Read-  |

| 0x14            | -                                  | FILTERE                               | D COUNT                                                                     | LS CHAN    | NEL 6 (LS                   | SB)              |                    |       |               | FILTERE                                                                     | D COUN      | TS CHAN              | NEL 6 (M    | SB)         |                |       |               | Only<br>Read-  |

| 0x15            | -                                  | LONG TE                               | ERM AVE                                                                     | RAGE CH    | HANNEL 6                    | (LSB)            |                    |       |               | LONG T                                                                      | ERM AVE     | RAGE CH              | ANNEL 6     | 6 (MSB)     |                |       |               | Only<br>Read-  |

| 0x16            |                                    | FILTERE                               | D COUNT                                                                     | LS CHAN    | NEL 7 (LS                   | SB)              |                    |       |               | FILTERE                                                                     | D COUN      | TS CHAN              | NEL 7 (M    | SB)         |                |       |               | Only<br>Read-  |

| 0x17            |                                    | LONG TE                               | ERM AVE                                                                     | RAGE CH    | HANNEL 7                    | (LSB)            |                    |       |               | LONG T                                                                      | ERM AVE     | RAGE CH              | ANNEL       | 7 (MSB)     |                |       |               | Only<br>Read-  |

| 0x18            | Channel Deltas                     | DELTA C                               | COUNTS                                                                      | CHANNEL    | L 0 (LSB)                   |                  |                    |       |               | DELTA C                                                                     | COUNTS      | CHANNEI              | _ 0 (MSB)   |             |                |       |               | Only<br>Read-  |

| 0x19            | (Signed value –<br>2's complement) | DELTA C                               | COUNTS                                                                      | CHANNEL    | L 1 (LSB)                   |                  |                    |       |               | DELTA (                                                                     | COUNTS      | CHANNEI              | _ 1 (MSB)   | 1           |                |       |               | Only<br>Read-  |

| 0x1A            | - ,                                | DELTA COUNTS CHANNEL 2 (LSB)          |                                                                             |            |                             |                  |                    |       |               | DELTA COUNTS CHANNEL 1 (MSB)<br>DELTA COUNTS CHANNEL 2 (MSB)                |             |                      |             |             |                |       |               | Only<br>Read-  |

| 0x1B            |                                    | DELTA COUNTS CHANNEL 3 (LSB)          |                                                                             |            |                             |                  |                    |       |               | DELTA COUNTS CHANNEL 2 (MSB)                                                |             |                      |             |             |                |       |               | Only<br>Read-  |

| 0x1C            | -                                  | DELTA COUNTS CHANNEL 4 (LSB)          |                                                                             |            |                             |                  |                    |       |               | DELTA COUNTS CHANNEL 4 (MSB)                                                |             |                      |             |             |                |       |               | Only<br>Read-  |

| 0x1D            | -                                  | DELTA COUNTS CHANNEL 5 (LSB)          |                                                                             |            |                             |                  |                    |       |               | DELTA COUNTS CHANNEL 5 (MSB)                                                |             |                      |             |             |                |       |               | Only<br>Read-  |

| 0x1E            | -                                  | DELTA COUNTS CHANNEL 6 (LSB)          |                                                                             |            |                             |                  |                    |       |               |                                                                             |             |                      |             |             |                |       | Only<br>Read- |                |

| 0x1E<br>0x1F    |                                    |                                       |                                                                             |            |                             |                  |                    |       |               | DELTA COUNTS CHANNEL 6 (MSB) DELTA COUNTS CHANNEL 7 (MSB)                   |             |                      |             |             |                |       |               | Only<br>Read-  |